面试必问题目,先记几个结论:

1.亚稳态会导致数字系统出现莫名其妙的故障

2.亚稳态这种现象不能绝对避免

(资料图片仅供参考)

(资料图片仅供参考)

3.满足寄存器Tsu和Th的采样,通常不会出现亚稳态现象

4.违反寄存器tsu或tH的采样不一定会导致亚稳态输出

5.亚稳态现象发生的概率不能消除,只能降低。

亚稳态这种现象是不可避免的,哪怕是在同步电路中也有概率出现,所以作为设计人员,我们能做的是减少亚稳态发生的概率。由于亚稳态而计算出的平均无故障工作时间 (MTBF)。设计人员是否应采取措施减少此类故障发生的机会。

以下拿爬山的小球作为例子解释。

左上的图,表示信号跳变时,已经超过了时钟沿后的保持时间了。这时触发器的输出还是旧值,可参考左下的时序图。

中上的图,表示信号跳变时,正好满足时钟沿的建立和保持时间。这时触发器的输出为新值,可参考中下的时序图。

右上的图,表示信号跳变时,不满足时钟沿的建立和保持时间。这时触发器的输出是亚稳态,可参考右下的时序图。

Figure 1. Metastability Illustrated as a Ball Dropped on a Hill

下图表示,亚稳态经过一段时间会稳定到新值或者旧值。也就是小球在山顶或者山腰会回落到山脚,要么是左边,要么是右边。

Figure 2. Examples of Metastable Output Signals

跨时钟域的经典处理方法就是多打两拍,也可以使用三拍或者更多拍的同步寄存器同步。

Figure 3. Sample Synchronization Register Chain

如上都是阐述的单bit跨时钟域的处理,而对于总线跨时钟的如何处理呢?我们下期再讲。

审核编辑:刘清

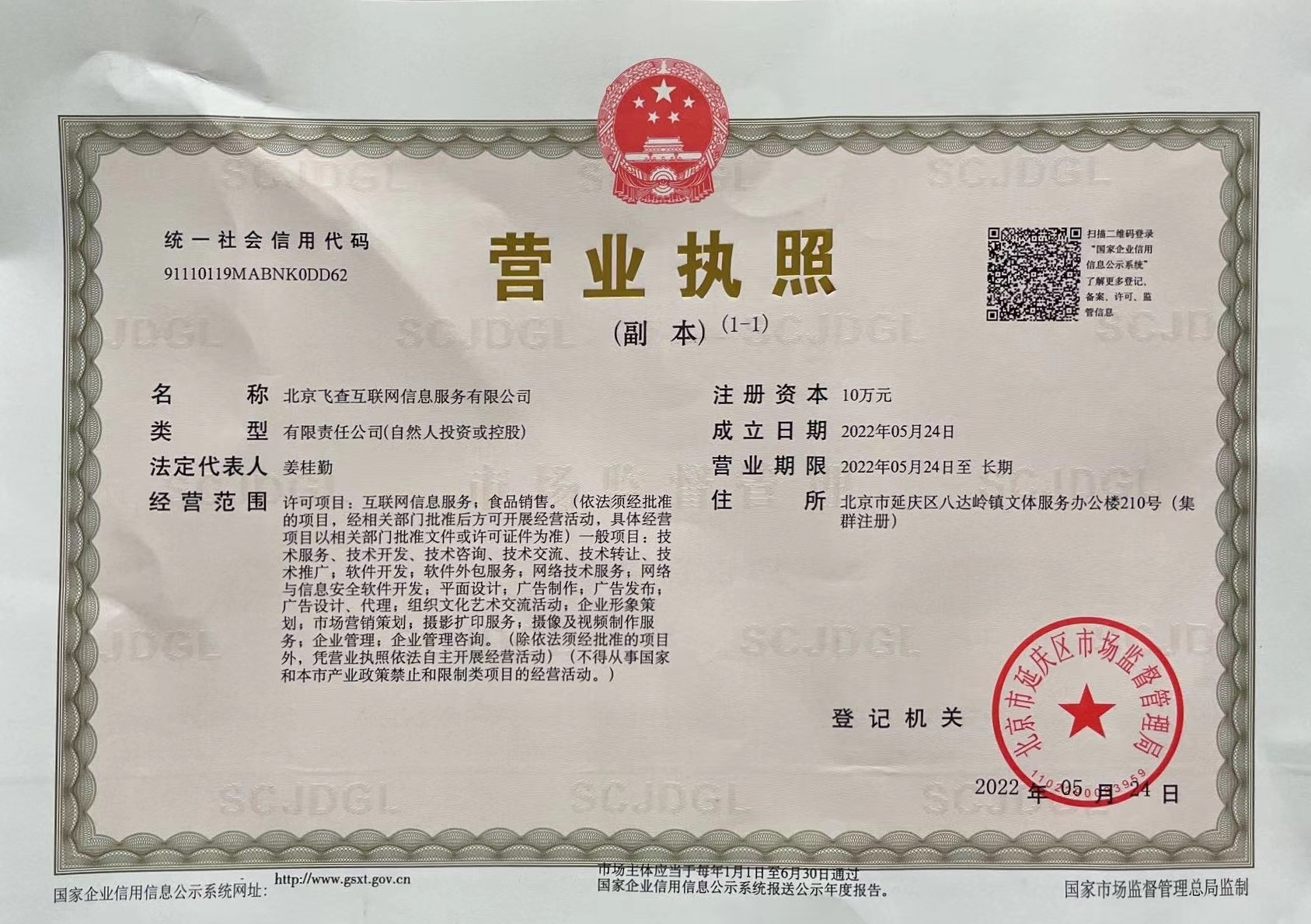

营业执照公示信息

营业执照公示信息